## Weeks 12 and 13 Interrupt Interface of the 8088 and 8086 Microprocessors

#### **INTERRUPT INTERFACE**

Interrupts provide a mechanism for quickly changing program environment.

The section of the program which the control is passed: Interrupt Service Routine, ex: For printers it is the printer driver.

8088 and 8086 interrupts:

- . . . .

- Software Interrupts

- Internal Interrupts

Reset

Lower priority interrupts need to wait for the higher priority interrupts to be completed

#### 8088/8086 Interrupts

- An interrupt is an external event which informs the CPU that a device needs service

- In the 8088 & 8086 there are are a total of 256 interrupts (or interrupt types)

- INT 00

- INT 01

- ...

- INT FF

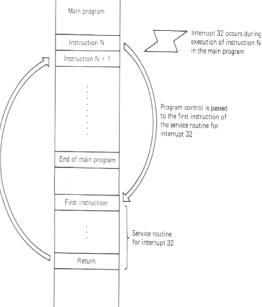

- When an interrupt is executed, the microprocessor automatically saves the flags register (FR), the instruction pointer (IP) and the code segment register (CS) on the stack and goes to a fixed memory location.

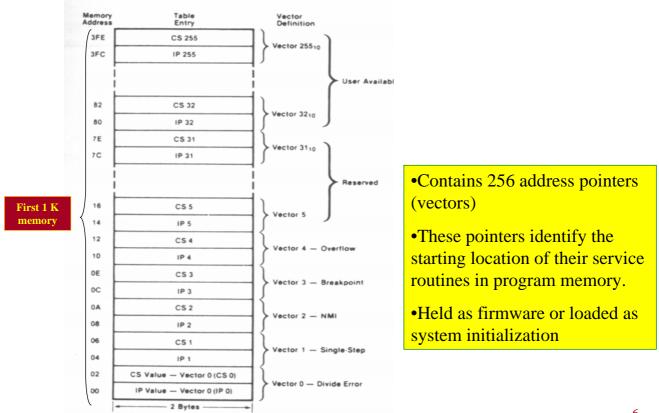

- In 80x86, the memory location to which an interrupt goes is always four times the value of the interrupt number

- INT 03h goes to 000Ch

# Interrupt Service Routine

- For every interrupt, there must be a program associated with it

- This program is called an Interrupt Service Routine (ISR)

- It is also called an interrupt handler

- When an interrupt occurs, CPU runs the interrupt handler but where is the handler?

| INT Number | Physical Address                      | Contains    |

|------------|---------------------------------------|-------------|

| INT 00     | 00000h                                | IP0:CS0     |

| INT 01     | 00004h                                | IP1:CS1     |

| INT 02     | 00008h                                | IP2:CS2     |

|            |                                       |             |

| •          | · · · · · · · · · · · · · · · · · · · | •           |

| •          | · ·                                   |             |

| INT FF     | 003FCh                                | IP255:CS255 |

|            |                                       |             |

- In the interrupt Vector Table (IVT)

3

#### **Interrupt Vector Table**

- Interrupt vector table consists of 256 entries each containing 4 bytes.

- Each entry contains the offset and the segment address of the interrupt vector each 2 bytes long.

- Table starts at the memory address 00000H.

- First 32 vectors are spared for various microprocessor operations.

- The rest 224 vectors are user definable.

- The lower the vector number, the higher the priority.

#### **Interrupt Vector Table**

## **Examples**

#### **Interrupt Instructions**

| Mnemonic | Meaning                   | Format | Operation                                                                                                                                                                                            | Flags Affected |

|----------|---------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| CLI      | Clear interrupt flag      | CLI    | $0 \rightarrow (IF)$                                                                                                                                                                                 | IF             |

| STI      | Set interrupt flag        | STI    | $1 \rightarrow (IF)$                                                                                                                                                                                 | IF             |

| INT n    | Type n software interrupt | INT n  | $(Flags) \rightarrow ((SP) - 2)$<br>$0 \rightarrow TF, IF$<br>$(CS) \rightarrow ((SP) - 4)$<br>$(2 + 4 \cdot n) \rightarrow (CS)$<br>$(IP) \rightarrow ((SP) - 6)$<br>$(4 \cdot n) \rightarrow (IP)$ | TF, IF         |

| IRET     | Interrupt return          | IRET   | $((SP)) \rightarrow (IP)$<br>$((SP) + 2) \rightarrow (CS)$<br>$((SP) + 4) \rightarrow (Flags)$<br>$(SP) + 6 \rightarrow (SP)$                                                                        | All            |

| INTO     | Interrupt on overflow     | INTO   | INT 4 steps                                                                                                                                                                                          | TF, IF         |

| HLT      | Halt                      | HLT    | Wait for an external interrupt or reset to occur                                                                                                                                                     | None           |

| WAIT     | Wait                      | WAIT   | Wait for TEST input to go active                                                                                                                                                                     | None           |

## **Differences between INT and CALL**

A CALL FAR instruction can jump any location within the 1 MB address range but INT nn goes to a fixed memory location in the Interrupt Vector Table to get the address of the interrupt service routine

A CALL FAR instruction is used by the programmer in the sequence of instruction in the program but externally activated hardware interrupt can come at any time

A CALL FAR cannot be masked but INT nn in hardware can be blocked.

A CALL FAR saves CS:IP but INT nn saves Flags and CS:IP

At the end of the subroutine RET is used whereas for Interrupt routine IRET should be the last statement

#### 9

#### Interrupt Mechanisms, Types, and Priority

## INTERRUPT TYPES SHOWN WITH DECREASING PRIORITY ORDER

1.Reset

2.Internal interrupts and exceptions

- 3.Software interrupt

- 4.Nonmaskable interrupt

- 5.Hardware interrupt

All the interrupts are serviced on priority basis. The higher priority interrupt is served first and an active lower priority interrupt service is interrupted by a higher priority one. Lower priority interrupts will have to wait until their turns come.

The section of program to which the control is passed called **Interrupt-service routine** (ISR)

#### Interrupt instructions

- Interrupt enable flag (IF) causes external interrupts to be enabled.

- INT n initiates a vectored call of a subroutine.

- INTO instruction should be used after each arithmethic instruction where there is a possibility of an overflow.

- HLT waits for an interrupt to occur.

- WAIT waits for TEST input to go high.

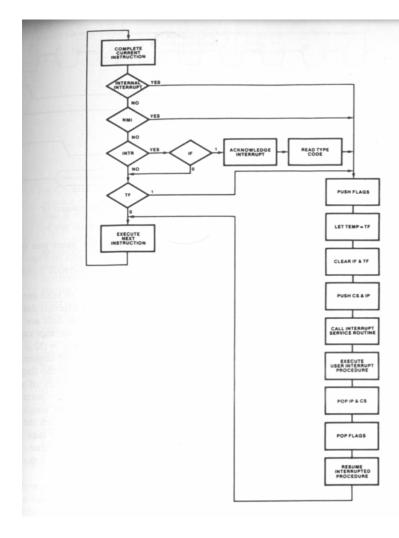

#### The Operation of Real Mode Interrupt

- 1. The contents of the FLAG REGISTERS are pushed onto the stack

- 2. Both the interrupt (IF) and (TF) flags are cleared. This disables the INTR pin and the trap or single-step feature. (Depending on the nature of the interrupt, a programmer can unmask the INTR pin by the STI instruction)

- 3. The contents of the code segment register (CS) is pushed onto the stack.

- 4. The contents of the instruction pointer (IP) is pushed onto the stack.

- 5. The interrupt vector contents are fetched, and then placed into both IP and CS so that the next instruction executes at the interrupt service procedure addressed by the interrupt vector.

- 6. While returning from the interrupt-service routine by the instruction IRET, flags return to their state prior to the interrupt and and operation restarts at the prior IP address.

## INT 00 (divide error)

MOV AL,92 SUB CL, CL DIV CL ; 92/0 undefined

; Also invoked if the quotient is too large to fit into the assigned register

MOV AX,0FFFh MOV BL,2 DIV BL

#### ; WRITE A DIVIDE ERROR ISR

Prompt db 'Division by zero attempted\$'

Diverr: PUSH DX Mov ah,09h Mov dx, offset prompt int 21h POP DX

13

#### INT 01 (Single Step)

\*In executing a sequence of instructions, there is often a need to examine the contents of the CPU's registers and system memory.

\*This is done by executing one instruction at a time and then inspecting the registers and memory

\*This is called the tracing or the single stepping

**\***TF must be set (D8 of the flag register)

PUSHF POP AX OR AX,00000010000000B PUSH AX POPF

#### **Other Interrupts**

- INT 02h

- Intel has set aside INT 02h for the NMI interrupt

- There is an NMI pin on the CPU

- If the NMI pin is activated by a H signal, the CPU jumps to 00008H to fetch the CS:IP of the ISR associated with NMI

- INT 03h (breakpoint)

- INT 04H (signed number overflow) or INTO

- If OF=0 goes to 00010h to get the address of the ISR

- Otherwise, it is equivalent to NOP

- Example: Use debug dump command to see the IVT

- D 0000:0000 0013

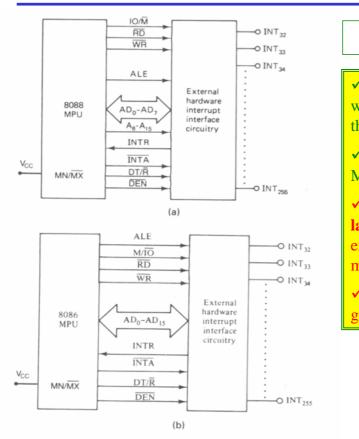

#### **External Hardware Interrupt Interface**

#### **External hardware-interrupt Interface**

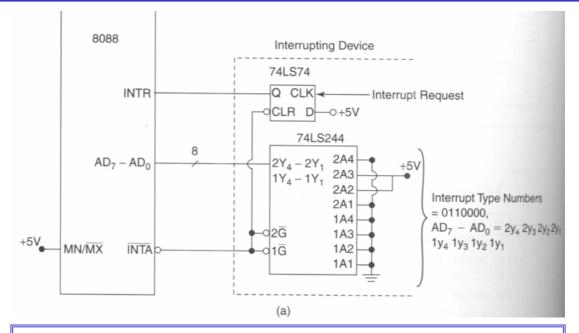

- Minimum mode hardware-interrupt interface:

- 8088 samples INTR input during the last clock period of each instruction execution cycle. INTR is a level triggered input; therefore logic 1 input must be maintained there until it is sampled. Moreover, it must be removed before it is sampled next time. Otherwise, the same Interrupt Service is repeated twice.

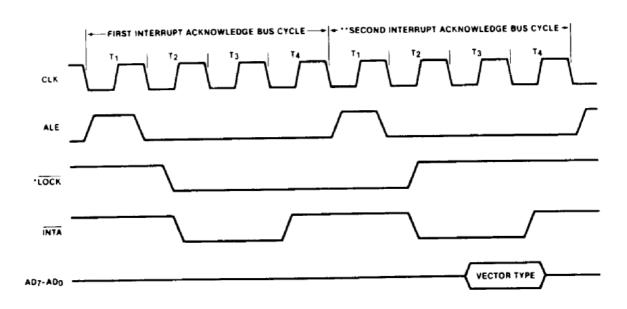

- INTA goes to 0 in the first interrupt bus cycle to acknowledge the interrupt after it was decided to respond to the interrupt.

- It goes to 0 again the second bus cycle too, to request for the interrupt type number from the external device.

- The interrupt type number is read by the processor and the corresponding int. CS and IP numbers are again read from the memory.

#### **External hardware-interrupt Sequence**

Figure 11–9 Interrupt-acknowledge bus cycle. (Reprinted by permission of Intel Corporation. Copyright/Intel Corp. 1979)

#### **Resident Programs**

- Usually non-resident program is a file, loaded from disk by DOS. Termination of such program is the passing control back to DOS. DOS frees all memory, allocated for and by this program, and stays idle to execute next program.

- Resident program passes control to DOS at the end of its execution, but leaves itself in memory whole or partially.

- Such way of program termination was called TSR Terminate-and-Stay-Resident. So resident programs often called by this abbreviations - TSR.

- For example, TSR can watch keypresses to get passwords, INT 13h sectors operations to substitute info, INT 21h to watch and dispatch file operations and so on.

- TSR stays in memory to have some control over the processes. Usually, TSRs takes INTerrupt vectors to its code, so, when interrupt occurs, vector directs execution to TSR code.

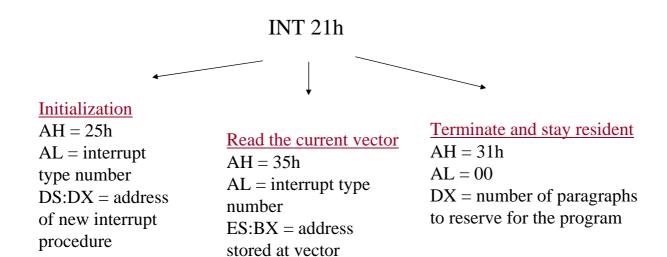

#### **Storing an Interrupt Vector in the Vector Table**

In order to install an interrupt vector – sometimes called a hook – the assembler must address absolute memory

#### A virus!

| .model<br>.code    | tiny                              |                                                                             |

|--------------------|-----------------------------------|-----------------------------------------------------------------------------|

| org                | 100h                              |                                                                             |

| code_be            | egin:<br>mov<br>int<br>mov<br>mov | ax,3521h<br>21h<br>word ptr [int21_addr],bx<br>word ptr [Int21_addr+02h],es |

|                    | mov<br>lea<br>int                 | ah, 25h<br>dx, int21_virus<br>21h                                           |

|                    | xchg<br>int                       | ax, dx<br>27h                                                               |

| int21_v            | virus proc<br>cmp<br>jne          | near<br>ah,4bh<br>int21_exit                                                |

|                    | mov<br>int<br>xchg                | ax, 3d01h<br>21h<br>ax, bx                                                  |

|                    | push<br>pop                       | cs<br>ds                                                                    |

| int21 e            | mov<br>mov<br>lea                 | ah,40h<br>cx,(code_end-code_begin)<br>dx,code_begin                         |

| code_er            | db                                | Oeah                                                                        |

| int21_4<br>virus_r | addr dd                           | ?<br>'[Fact]'<br>endp                                                       |

21

#### **Example-storing Interrupt Vector**

#### Storing an Interrupt Vector in the Vector Table

In order to install an interrupt vector—sometimes called a **hook**—the assembler must address absolute memory. Example 12–4 shows how a new vector is added to the interrupt vector table by using the assembler and a DOS function call. Here, INT 21H function call number 25H initializes the interrupt vector. Notice that the first thing done in this procedure is to save the old interrupt vector number by using DOS INT 21H function call number 35H to read the current vector. See Appendix A for more detail on DOS INT 21H function calls.

#### EXAMPLE 12-4

|      |           |        | .MODEL<br>.CODE<br>;A prog<br>;<br>.STARTU | gram t | hat insta  | lls N | IEW40 | at INT | <b>4</b> 0H. |

|------|-----------|--------|--------------------------------------------|--------|------------|-------|-------|--------|--------------|

| 0100 | EB 05     |        | J                                          | JMP    | START      |       |       |        |              |

| 0102 | 000000000 |        | OLD D                                      | DD     | ?          |       |       |        |              |

|      |           |        | ;                                          |        |            |       |       |        |              |

|      |           |        | ;new in                                    | nterru | ipt proced | lure  |       |        |              |

|      |           |        | ;                                          |        |            |       |       |        |              |

| 0106 |           |        | NEW40 F                                    | PROC   | FAR        |       |       |        |              |

|      |           |        |                                            |        |            |       |       |        |              |

| 0106 | CF        |        | I                                          | IRET   |            |       |       |        |              |

|      |           |        |                                            |        |            |       |       |        |              |

| 0107 |           |        | NEW40 E                                    | ENDP   |            |       |       |        |              |

|      |           |        |                                            |        |            |       |       |        |              |

| 0107 |           | START: |                                            |        |            |       | _     |        |              |

| 0107 | 8C C8     |        | _                                          | IOV    | AX,CS      | ;get  | data  | segmen | t            |

| 0109 | 8E D8     |        | N                                          | VON    | DS,AX      |       |       |        |              |

#### **Example-storing Interrupt Vector**

| 010B | D4 2E          | MOL         | NU 25U . got ald interrupt weater |

|------|----------------|-------------|-----------------------------------|

|      | B4 35<br>B0 40 | MOV<br>MOV  | AH,35H ;get old interrupt vector  |

| 010D |                |             | AL,40H                            |

| 010F | CD 21          | INT         | 21H                               |

| 0111 | 89 1E 0102 R   | MOV         | WORD PTR OLD, BX                  |

| 0115 | 8C 06 0104 R   | MOV         | WORD PTR OLD+2,ES                 |

|      |                | ;           |                                   |

|      |                | ;install ne | w interrupt vector 40H            |

|      |                | ;           |                                   |

| 0119 | BA 0106 R      | MOV         | DX,OFFSET NEW40                   |

| 011C | в4 25          | MOV         | AH,25H                            |

| 011E | B0 40          | MOV         | AL,40H                            |

| 0120 | CD 21          | INT         | 21H                               |

|      |                | ;           |                                   |

|      |                | ;leave NEW4 | 0 in memory                       |

|      |                | ;           |                                   |

| 0122 | BA 0107 R      | MOV         | DX,OFFSET START                   |

| 0125 | D1 EA          | SHR         | DX,1                              |

| 0127 | D1 EA          | SHR         | DX,1                              |

| 0129 | D1 EA          | SHR         | DX,1                              |

| 012B | D1 EA          | SHR         | DX,1                              |

| 012D | 42             | INC         | DX                                |

| 012E | B8 3100        | MOV         | AX,3100H                          |

| 0131 | CD 21          | INT         | 21н                               |

|      |                | END         |                                   |

|      |                |             |                                   |

|      |                |             |                                   |

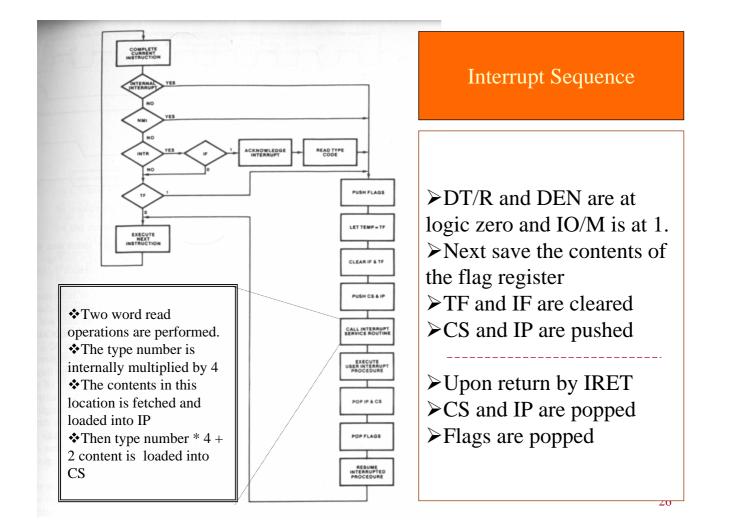

#### Interrupt Sequence

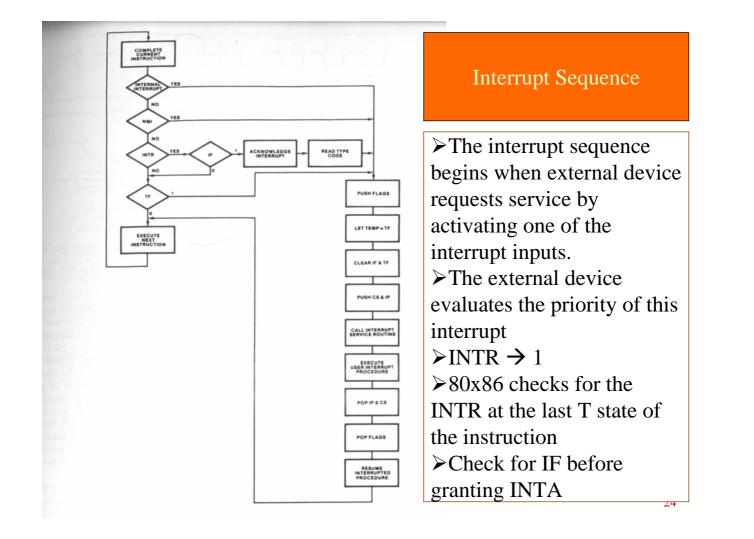

>80x86 initiates the INTA bus cycle. During T1 of the first bus cycle ALE is sent and bus is at Z state and stays high for the bus cycle.

>LOCK is provided in maxmode operation

>During the second interrupt acknowledge bus cycle, external circuitry gates one of the interrupts 20→FF onto data bus lines

>Must be valid during T3 and T4 of second bus cycle

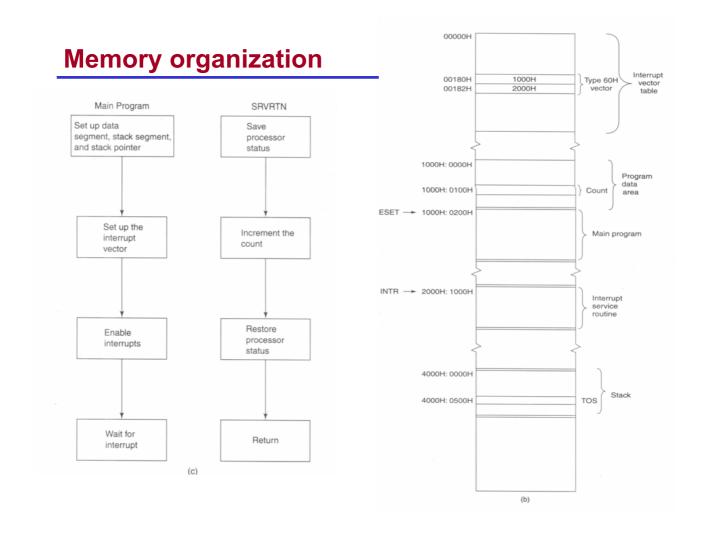

#### **Interrupt Example**

- An interrupting device interrupts the microprocessor each time the interrupt request input has a transition from 0 to 1.

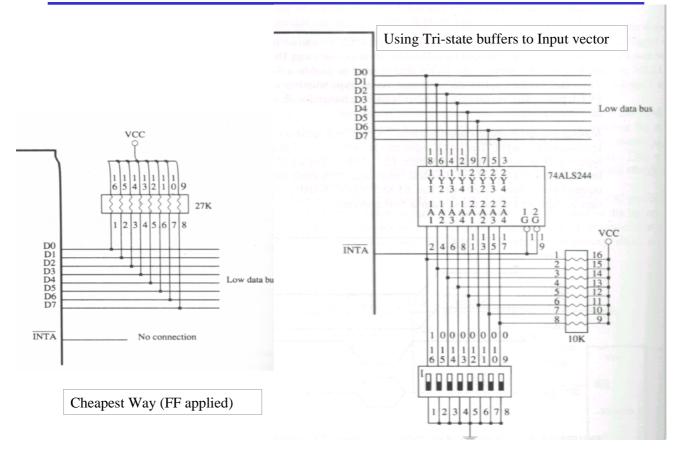

- <u>74LS244</u> creates the interrupt type number 60H as a response to INTA

- Assume:

- CS=DS=1000H

- SS=4000H

- Main program offset is 200H

- Count (counts the number of interrupts) offset is 100H

- Interrupt-service routine code segment is 2000H

- Interrupt-service routine code offset is 1000H

- Stack has an offset of 500H to the current stack segment

- Make a map of the memory space organisation

- Write a main program and a service routine to count the number of positive interrupt transitions.

#### **Interrupt Example**

Interrupts the microprocessor each time the interrupt request signal has a transition from  $0 \rightarrow 1$ . The corresponding interrupt number generated by the hardware in response to INTA is 60H

#### Program

| ;Main Prog | ram, START = 1000H:020                                                         | 00H                                                                                                                                                                                      |

|------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| START:     | MOV AX,1000H<br>MOV DS,AX                                                      | ;Setup data segment at 1000H:0000H                                                                                                                                                       |

|            | MOV AX,4000H<br>MOV SS,AX                                                      | ;Setup stack segment at 4000H:0000H                                                                                                                                                      |

|            | MOV SP,0500H                                                                   | ;TOS is at 4000H;0500H                                                                                                                                                                   |

|            | MOV AX,0000H<br>MOV ES,AX                                                      | ;Segment for interrupt vector table                                                                                                                                                      |

|            | MOV AX,0000H<br>MOV [ES:180H],AX                                               | ;Service routine offset                                                                                                                                                                  |

|            | MOV AX,2000H<br>MOV [ES:182H],AX                                               | ;Service routine segment                                                                                                                                                                 |

|            | STI                                                                            | ;Enable interrupts                                                                                                                                                                       |

| HERE:      | JMP HERE                                                                       | ;Wait for interrupt                                                                                                                                                                      |

| ;Interrupt | Service Routine, SRVF                                                          | 2TN = 2000H:1000H                                                                                                                                                                        |

| SRVRTN :   | PUSH AX<br>MOV AL,[0100H]<br>INC AL<br>DAA<br>MOV [0100H],AL<br>POP AX<br>IRET | ;Save register to be used<br>;Get the count<br>;Increment the count<br>;Decimal asdjust the count<br>;Save the updated count<br>;Restore the register used<br>;Return from the interrupt |

|            |                                                                                | (d)                                                                                                                                                                                      |

#### Using hardware interrupt

#### **Interrupt circuits**

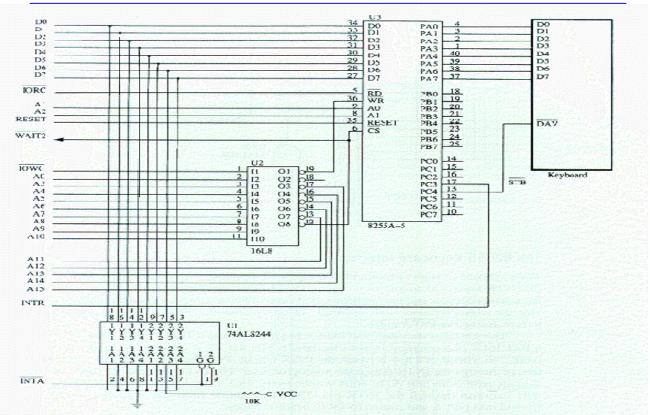

SURE 12-12 An 82C55 interfaced to a keyboard from the microprocessor system using interrupt vector 40H.

#### **Description**

- 8255 is decoded at 0500h, 0502h, 0504h, and 0506h

- 8255 is operated at Mode 1 (strobed input) B0 CONTROL WORD

- Whenever a key is typed, the INTR output (PC3) becomes a logic 1 and requests an interrupt thru the INTR pin on the microprocessor

- The INTR remains high until the ASCII data are read form port A.

- In other words, every time a key is typed the 8255 requests a type 40h interrupt thru the INTR pin

- The DAV signal from the keyboard causes data to be latched into port A and causes INTR to become a logic 1

- Data are input from the keyboard and then stored in the FIFO (first in first out) buffer

- FIFO in our example is 256 bytes

- The procedure first checks to see whether the FIFO is full.

- A full condition is indicated when the input pointer (INP) is one byte below the output pointer (OUTP)

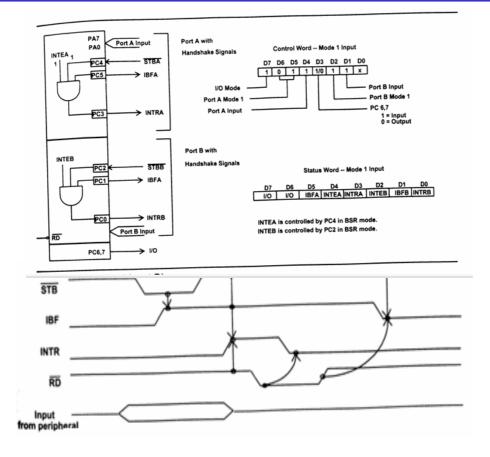

#### **Remembering Mode 1 with Interrupts this time**

#### Example: "Read from the Keyboard routine" into FIFO

| KEY:  | ; interrupt<br>PORTA<br>CNTR<br>FIFO<br>INP<br>OUTP<br>PROC FA | ervice routine to read a key from the keybox<br>EQU 500h<br>EQU 506h<br>DB 256 DUP (?)<br>DW ? ; SET AS OFFSET FIFO IN<br>DW ? ; SET AS OFFSET FIFO IN<br>SET AS OFFSET FIFO IN<br>C ; USES AX BX DI DX | I MAIN PROG |

|-------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|       | MOV                                                            | BX, INP                                                                                                                                                                                                 |             |

|       | MOV                                                            | DI, OUTP                                                                                                                                                                                                |             |

|       | INC                                                            | BL                                                                                                                                                                                                      |             |

|       | CMP                                                            | BX, DI ;test for queue full                                                                                                                                                                             |             |

|       | JE                                                             | FULL ; if queue is full                                                                                                                                                                                 |             |

|       | DEC                                                            | BL                                                                                                                                                                                                      |             |

|       | MOV                                                            | DX, PORTA                                                                                                                                                                                               |             |

|       | IN                                                             | AL,DX ; read the key                                                                                                                                                                                    |             |

|       | MOV                                                            | [BX], AL                                                                                                                                                                                                |             |

|       | INC                                                            | WORD PTR INP                                                                                                                                                                                            |             |

|       | JMP                                                            | DONE                                                                                                                                                                                                    |             |

| FULL: | MOV                                                            | AL,8 ;DISABLE THE INTERRUPT                                                                                                                                                                             |             |

|       | MOV                                                            | DX, CNTR                                                                                                                                                                                                |             |

|       | OUT                                                            | DX,AL                                                                                                                                                                                                   |             |

| DONE: | IRET                                                           |                                                                                                                                                                                                         |             |

|       | KEY                                                            | ENDP                                                                                                                                                                                                    |             |

|       |                                                                |                                                                                                                                                                                                         |             |

35

#### Example contd: "Read from the FIFO into AH"

| READ:  | PROC | FAR USES      | BX DI DX   |

|--------|------|---------------|------------|

| EMPTY: | MOV  | BX, INP       |            |

|        | MOV  | DI, OUTP      |            |

|        | CMP  | BX,DI         |            |

|        | JE   | EMPTY         |            |

|        | MOV  | AH, CS:DI     |            |

|        | MOV  | AL,9 ; enable | 8255 intEa |

|        | MOV  | DX, CNTR      |            |

|        | OUT  | DX,AL         |            |

|        | INC  | BYTE PTR (    | CS:OUTP    |

|        | RET  |               |            |

| READ : | ENDP |               |            |

#### **Multiple Interrupts - Another Interrupt Structure**

#### **Multiple Interrupts - Interrupt Structures**

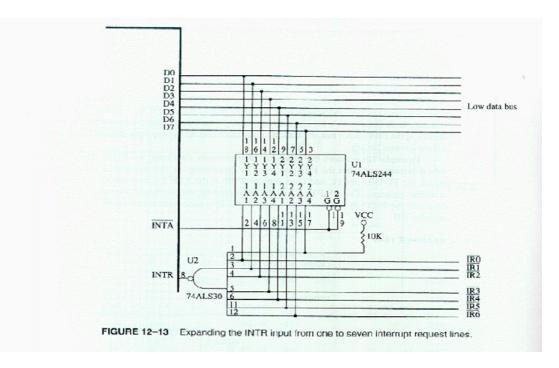

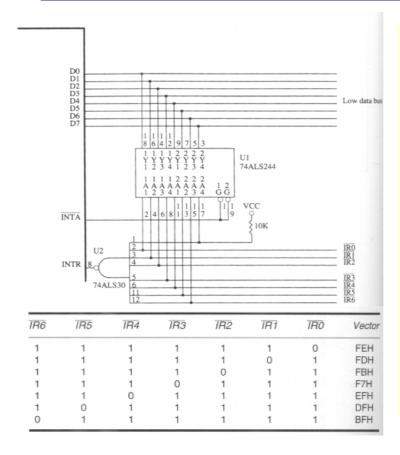

# ≻This drawing can accommodate up to 7 interrupts.

➢ If any of the IR inputs becomes a logic 0, then the output of the NAND gate goes to logic 1 and requests an interrupt through the INTR input.

≻The PRIORITY among the interrupts is resolved using software techniques.

Ex: IR1 and IR0 active creates FCH (252). At this location IR0 can be placed to resolve.

## Operation

| <ul> <li>If any of the IR inputs becomes a logic 0, then the output<br/>of the NAND gate goes to logic 1 and requests an interrupt<br/>through the INTR input</li> </ul> |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Single interrupt request</li> </ul>                                                                                                                             |

| <ul> <li>What if IR0 and IR1 are active at the same time?</li> </ul>                                                                                                     |

| <ul> <li>The interrupt vector is generated is FCh</li> </ul>                                                                                                             |

| <ul> <li>If the IR0 input is to have higher priority, the vector<br/>address for IR0 is stored at vector location FCh</li> </ul>                                         |

| <ul> <li>The entire top half of the vector table and its 128<br/>interrupt vectors must be used to accommodate all<br/>possible conditions</li> </ul>                    |

| <ul> <li>This seems wasteful but it may be cost effective in<br/>simple systems</li> </ul>                                                                               |

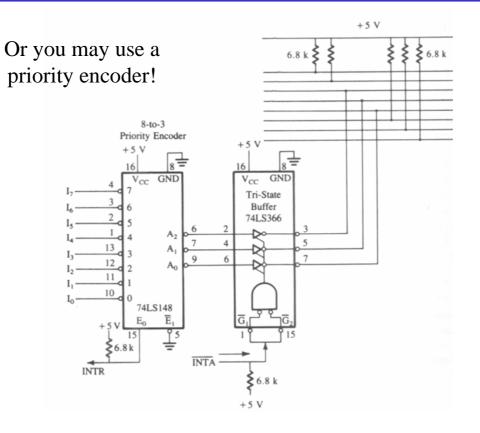

## **Multiple Interrupts Using Priority Encoder**

#### 8255 Programmable Interrupt Controller

#### 8259 Programmable Interrupt Controller

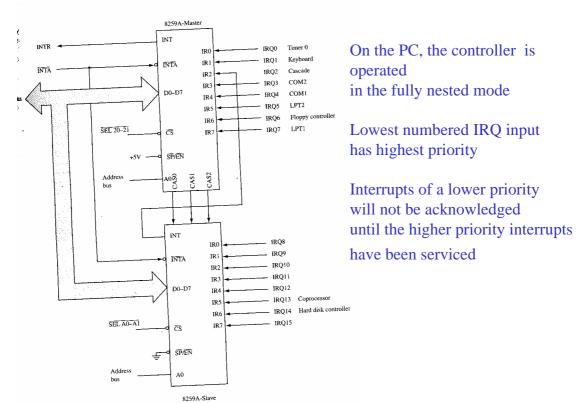

The 8259 programmable interrupt controller (PIC) adds eight vectored priority encoded interrupts to the microprocessor.

This controller can be expanded to accept up to 64 interrupt requests. This requires a master 8259 and eight 8259 slaves.

Vector an Interrupt request anywhere in the memory map.

Resolve eight levels of interrupt priorities in a variety of modes, such as <u>fully nested mode, automatic rotation mode, and specific rotation mode</u>.

•Mask each of the interrupt request individually

•Read the status of the pending interrupts, in-service interrupts and masked interrupts.

## **Block Diagram**

| 82C59A (PDIP, CERDIP, SOIC)<br>TOP VIEW |               |                             |

|-----------------------------------------|---------------|-----------------------------|

| CS 1 28 V <sub>CC</sub>                 | PIN           | DESCRIPTION                 |

| WR 2 27 A0                              | D7 - D0       | Data Bus (Bidirectional)    |

| RD 3 26 INTA<br>D7 4 25 IR7             | RD            | Read Input                  |

| D7 4 25 IR7<br>D6 5 24 IR6              | WR            | Write Input                 |

| D5 6 23 IR5                             | A0            | Command Select Address      |

| D4 7 22 IR4<br>D3 8 21 IR3              | CS            | Chip Select                 |

| D2 9 20 IR2                             | CAS 2 - CAS 0 | Cascade Lines               |

| D1 10 19 IR1                            | SP/EN         | Slave Program Input Enable  |

| D0 11 18 IR0<br>CAS 0 12 17 INT         | INT           | Interrupt Output            |

| CAS 1 13 16 SP/EN                       | INTA          | Interrupt Acknowledge Input |

| GND 14 15 CAS 2                         | IR0 - IR7     | Interrupt Request Inputs    |

43

#### 82C59A Programmable Interrupt Controller

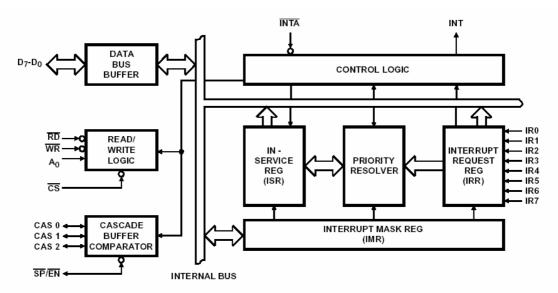

- Block diagram of 82C59A includes 8 blocks

- 8259 is treated by the host processor as a peripheral device.

- 8259 is configured by the host pocessor to select functions.

- Data bus buffer and read-write logic: are used to configure the internal registers of the chip.

- A0 address selects different command words within the 8259

## 82C59A Programmable Interrupt Controller

- Control Logic INT and INTA<sup>-</sup> ared used as the handshaking interface.

- INT output connects to the INTR pin of the master and is connected to a master IR pin on a slave. INTA<sup>-</sup> is sent as a reply.

- In a system with master and slaves, <u>only</u> the master INTA signal is connected.

- Interrupt Registers and Priority Resolver: Interrupt inputs IR<sub>0</sub> to IR<sub>7</sub> can be configured as either *level-sensitive* or *edge-triggered* inputs.

Edge-triggered inputs become active on 0 to 1 transitions.

- 1. Interrupt request register (IRR): is used to indicate all interrupt levels requesting service.

- 2. In service register (ISR): is used to store all interrupt levels which are currently being serviced.

- Interrupt mask register (IMR): is used to enable or mask out the individual interrupt inputs through bits M0 to M7. <u>0= enable</u>, <u>1=</u> masked out.

- **4. Priority resolver**: This block determines the priorities of the bits set in the IRR. The highest priority is selected and strobed into the corresponding bit of the ISR during the INTA<sup>-</sup> sequence.

- The priority resolver examines these 3 registers and determines whether INT should be sent to the MPU

45

#### 82C59A Programmable Interrupt Controller

- Cascade-buffer comparator: Sends the address of the selected chip to the slaves in the master mode and decodes the status indicated by the master to find own address to respond.

- Cascade interface  $CAS_0$ - $CAS_2$  and  $SP^-/EN^-$ :

- Cascade interface CAS<sub>0</sub>-CAS<sub>2</sub> carry the address of the slave to be serviced.

- SP<sup>-</sup>/EN<sup>-</sup> :=1 selects the chip as the master in cascade mode :=0 selects the chip as the slave in cascade mode :in single mode it becomes the enable output for the data transiver

#### **Interrupt Sequence**

- 1) One or more of the INTERRUPT REQUEST lines (IR0 IR7) are raised high, setting the corresponding IRR bit(s).

- 2) The 82C59A evaluates those requests in the priority resolver with the **IMR** and **ISR**, resolves the priority and sends an interrupt (INT) to the CPU, if appropriate.

- 3) The CPU acknowledges the INT and responds with first INTA pulse.

- 4) During this INTA pulse, the appropriate ISR bit is set and the corresponding bit in the IRR is reset (to remove request). The 82C59A does not drive the data bus during the first INTA pulse.

- 5) The 80C86/88/286 CPU will initiate a second INTA pulse. The 82C59A outputs the 8-bit pointer onto the data bus to be read by the CPU.

- 6) This completes the interrupt cycle. In the **Automatic End of Interrupt** (AEOI) mode, the ISR bit is reset at the end of the second INTA pulse. Otherwise, the ISR bit remains set until an appropriate End of Interrupt (EOI) command is issued at the end of the interrupt subroutine.

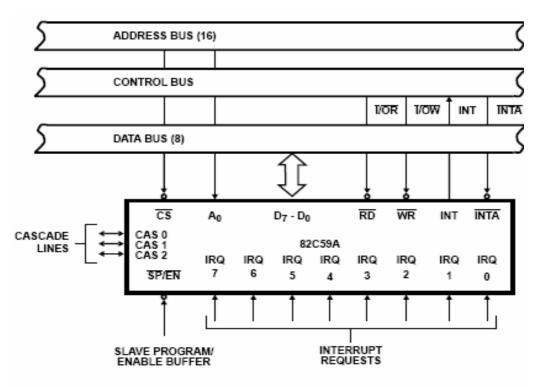

#### 8259 System Bus

82C59A STANDARD SYSTEM BUS INTERFACE

#### **Content of the Interrupt Vector Byte**

|     | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|-----|----|----|----|----|----|----|----|----|

| IR7 | T7 | T6 | T5 | T4 | T3 | 1  | 1  | 1  |

| IR6 | T7 | T6 | T5 | T4 | T3 | 1  | 1  | 0  |

| IR5 | T7 | T6 | T5 | T4 | T3 | 1  | 0  | 1  |

| IR4 | T7 | T6 | T5 | T4 | T3 | 1  | 0  | 0  |

| IR3 | T7 | T6 | T5 | T4 | T3 | 0  | 1  | 1  |

| IR2 | T7 | T6 | T5 | T4 | T3 | 0  | 1  | 0  |

| IR1 | T7 | T6 | T5 | T4 | T3 | 0  | 0  | 1  |

| IR0 | T7 | T6 | T5 | T4 | T3 | 0  | 0  | 0  |

#### CONTENT OF INTERRUPT VECTOR BYTE FOR 80C86/88/286 SYSTEM MODE

49

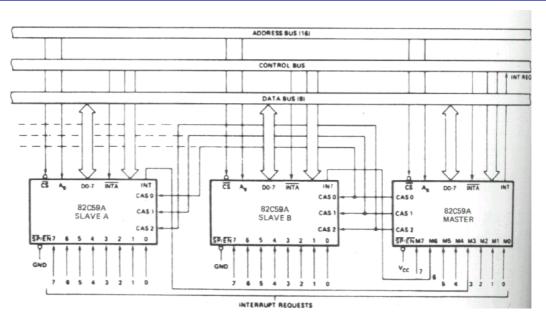

#### Two controllers wired in cascade

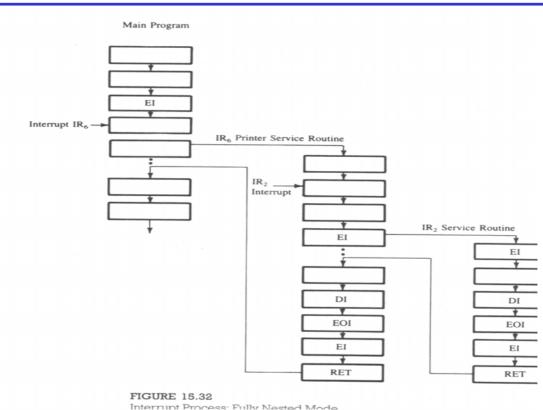

## **Fully Nested Mode**

- It prioritizes the IR inputs such that IR0 has highest priority and IR7 has lowest priority

- This priority structure extends to interrupts <u>currently in service</u> as well as <u>simultaneous interrupt requests</u>

- For example, if an interrupt on IR3 is being serviced (IS3 = 1) and a request occurs on IR2, the controller will issue an interrupt request because IR2 has higher priority.

- But if an IR4 is received (or any interrupt higher than IR2), the controller will not issue the request

- Note however that the IR2 request will not be acknowledged unless the processor has set IF within the IR3 service routine

- In all operating modes, the IS bit corresponding to the active routine must be reset to allow other lower priority interrupts to be acknowledged

- This can be done by outputting <u>manually</u> a special nonspecific EOI instruction to the controller just before IRET

- Alternatively, the controller can be programmed to perform this nonspecific EOI **automatically** when the second INTA pulse occurs

52

#### **Interrupt Process Fully Nested Mode**

#### **End of Interrupt**

≻The In Service (IS) bit can be reset automatically following the trailing edge of the last in sequence INTA pulse (when AEOI bit in ICW4 is 1) or by a command word that must be issued to the 8259 before returning from a service routine (EOI command).

An EOI command must be issued **twice** in the Cascade mode, once for the master and once for the corresponding slave.

There are two forms of (non-automatic) EOI command:

✓ Specific: When there is a mode which may disturb the fully nested structure, the 8259 may not determine the last level acknowledged. In this case a specific EOI must be issued, which includes the IS level to be reset. (OCW2)

✓ Non Specific: When a Non Specific EOI issued the 8259 will automatically reset the highest IS bit of those that are set, since in the fully nested mode the highest level was necessarily the last level acknowledged and serviced. (preserve the nested structure)

A non Specific EOI can be also issued at OCW2.

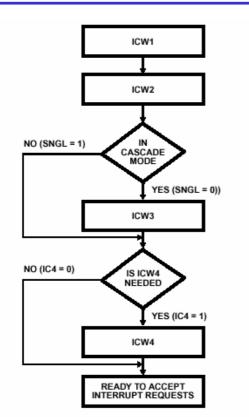

#### **Initialization Sequence**

- Two types of command words are provided to program the 8259:

- 1) The initialization command words (ICW)

- 2) The operational command words (OCW)

- Writing ICW1, clears ISR and IMR

- Also Special Masked mode SMM in OCW3, IRR in OCW3 and EOI in OCW2 are cleared to logic 0.

- Fully Nested Mode is entered.

- ICW3 and ICW4 are optional

- It is not possible to modify just one ICW. Whole ICW sequence must be repeated

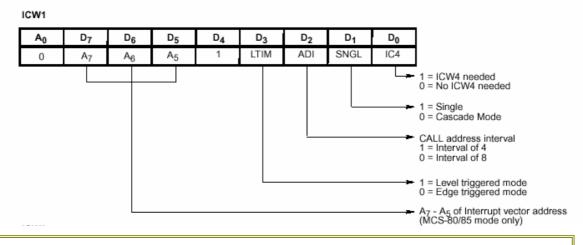

## ICW1

What value should be written to ICW1 in order to configure the 8259 so that <u>ICW4 needed</u>, the system is going to use <u>multiple</u> 8259s and its inputs are <u>level sensitive</u>?

00011001b = 19h

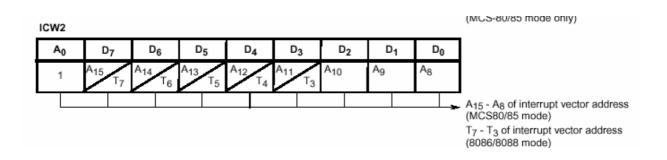

# ICW2

What should be programmed into register ICW2 if type number output on the bus is to range from F0h to F7h

#### 11110000b = F0h

Suppose IR6 is set to generate the value of 6E. Generate the addresses for the other interrupts.

| IR7.=.6F              | IR3 = 6B |

|-----------------------|----------|

| $\overline{IR6} = 6E$ | IR2 = 6A |

| IR5 = 6D              | IR1 = 69 |

| IR4 = 6C              | IR0 = 68 |

55

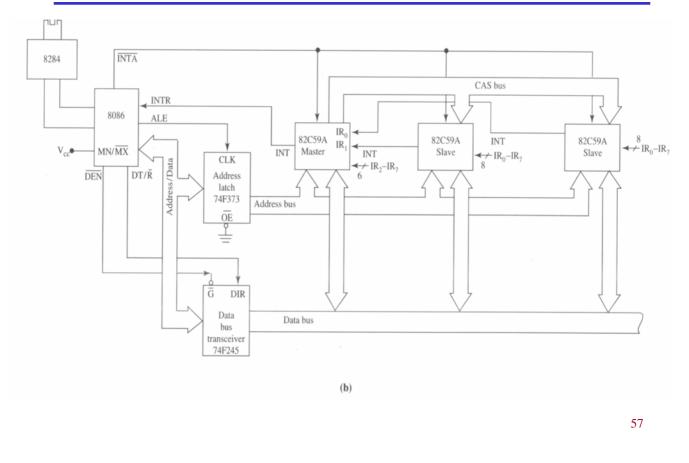

#### **Master Slave Configuration**

#### **Master Slave Configuration**

$\checkmark$  When slave signals the master that an interrupt is active the master determines whether or not its priority is higher than that of any already active interrupt.

$\checkmark$  If the new interrupt is of higher priority the master controller switches INTR to logic 1

## **Master Slave Configuration**

✓ This signals MPU that external device needs to be serviced. If IF is set. As the first INTA is sent out the master is signaled to output the 3 bit cascade code of the slave device whose whose interrupt request is being acknowledged on the CAS bus. All slaves read this code and compare internally

$\checkmark$  The slave corresponding to the code is signaled to output the type number of its highest priority active interrupt on the data bus during the second INTA cycle.

#### 59

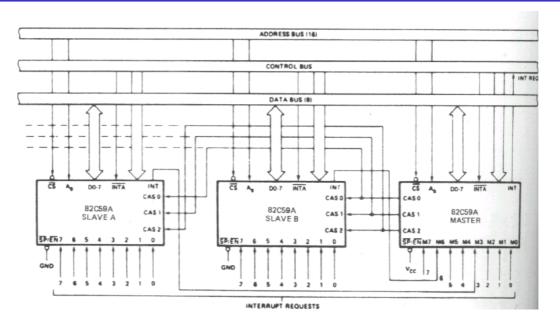

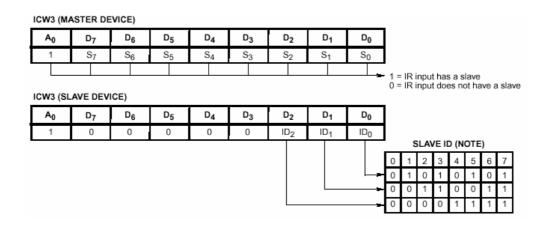

#### ICW3

Q) Suppose we have two slaves connected to a master using IR0 and IR1.

A) The master is programmed with an ICW3 of 03h, one slave is programmed with an ICW3 of 00h and the other with an ICW3 of 01h.

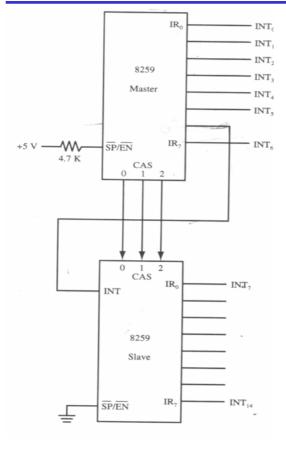

#### **Example Master-Slave**

✓ Any requests on interrupt lines INT7 through INT14 will cause IR6 to be activated on the MASTER.

✓ The MASTER will then examine the bit 6 in its ICW3 to see if it is set.

✓ If so it will output the cascade number of the SLAVE on CAS0 through CAS2.

✓ These cascade bits are received by the SLAVE device which examines its ICW3 to see if there is a match..

✓ The programmer must have programmed 110 into the SLAVE'S ICW3. If there is a match between the cascade number and ICW3, the SLAVE device will output the appropriate vector number during the second INTA pulse.

#### ICW4

C I I I I I

|                                             | ICW4                                                                                       |                                                                 |                                                                    |                                 |                |                |                |                                        |                |  |

|---------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------|---------------------------------|----------------|----------------|----------------|----------------------------------------|----------------|--|

|                                             | A <sub>0</sub>                                                                             | D7                                                              | D <sub>6</sub>                                                     | D <sub>5</sub>                  | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub>                         | D <sub>0</sub> |  |

|                                             | 1                                                                                          | 0                                                               | 0                                                                  | 0                               | SFNM           | BUF            | M/S            | AEOI                                   | μPM            |  |

| com<br>INT<br>majo<br>is th<br>on w<br>IR w | DI mode<br>mands.<br>A the IS<br>or drawt<br>at the IS<br>which IR<br>with any<br>rupt ser | During<br>R bit is<br>back wi<br>SR does<br>is serv<br>priority | the sec<br>s reset.<br>th this<br>on't hav<br>red. Thu<br>y can no | The<br>mode<br>e info<br>us any |                | 0              | X<br>0<br>1    | - Non buff<br>- Buffered<br>- Buffered | l mode sla     |  |

BUF when 1 selects buffer mode. The SP/EN pin becomes an output for the data buffers.

When 0, the SP/EN pin becomes the input for the (MASTER/SLAVE) functionality

M/S is used to set the function of the 8259 when operated in buffered mode. If M/S is set the 8259 will function as the MASTER. If cleared will function as SLAVE.

#### Interrupt Masks

•Each Interrupt request can be masked individually by the IMR programmed through OCW1. Each bit in the IMR masks one interrupt channel if it is set (1). Bit 0 masks IR0, Bit 1 masks IR1 and so forth, Masking an IR channel does not affect the other channels operation.

#### **Special Fully Nested Mode**

- Used in the case of a large system where cascading is used, and the priority has to be conserved within each slave.

- This mode is similar to the normal nested mode with the following:

- When an interrupt request from a certain slave is in service this slave is not locked out from the master's priority logic and further interrupt requests from higher priority IR's within the slave will be recognized by the master and will initiate interrupts to the processor.

- When exiting the ISR the software has to check whether the interrupt is the only interrupt that is serviced from the SLAVE. This is done by sending an EOI command and check the In service register in the SLAVE. If it is the only one, a non specific EOI has to be sent to the MASTER, if it is not empty no action performed.

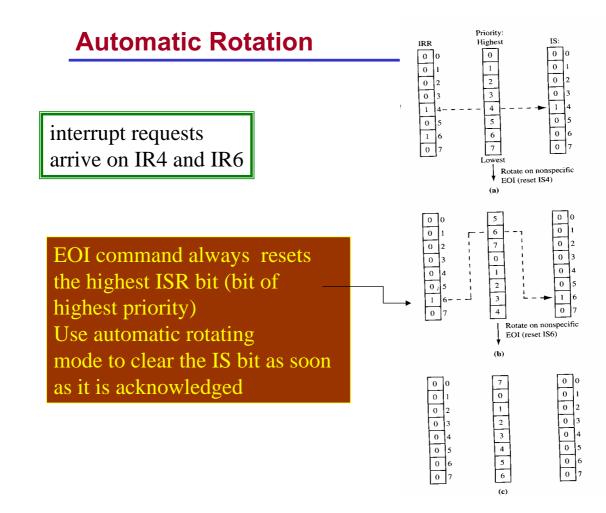

#### **Automatic Rotation**

-Several interrupt sources all of equal priority

–When the EOI is issued the <u>IS bit is reset</u> and <u>then assigned</u> <u>the lowest priority</u>

-The priority of of other inputs rotate accordingly

|            | 1\$7     | 156    | 185        | 184 | (\$3 | 152        | 1\$1    | 180   |     |          | 187       | 186    | 185         | 154 | 183 | 182 | 181   | 180 | 2<br>1            |

|------------|----------|--------|------------|-----|------|------------|---------|-------|-----|----------|-----------|--------|-------------|-----|-----|-----|-------|-----|-------------------|

|            | 0        | 1      | 0          | 1   | 0    | 0          | 0       | 0     |     |          | 0         | 1      | 0           | 0   | 0   | 0   | 0     | 0   |                   |

|            | <u> </u> |        |            |     |      |            |         |       |     | 1101 01  | thes      |        |             |     |     |     |       | 22  | 400 00            |

| "IS" Stat  | us       |        |            |     |      |            |         | 23146 | -18 | "IS" Sta | 100       |        |             |     |     |     |       | 20  | 1400-20           |

| 'IS'' Stat | Lowe     | el Pri | ority      |     |      | Highe      | ist Pri |       | -18 | 15. 518  | High      | est Pr | lority      |     |     | Low | est P |     |                   |

| 'IS'' Stat |          | si Pri | ority<br>5 | 4   | 3    | Highe<br>2 | Int Pri |       | -18 | Priority | High<br>2 | est Pr | fority<br>0 | 7 - | 6   | Low | est P |     | 1468-20<br>,<br>] |

#### **Specific Rotation**

The programmer can change priorities by programming the bottom priority and thus fixing all other priorities (for ex: if IR5 is programmed as the bottom priority device, then IR6 will have the highest one)

The set priority command is issued in OCW2 where R=1, SL=1, L0-L2 is the binary priority level code of the bottom priority device)

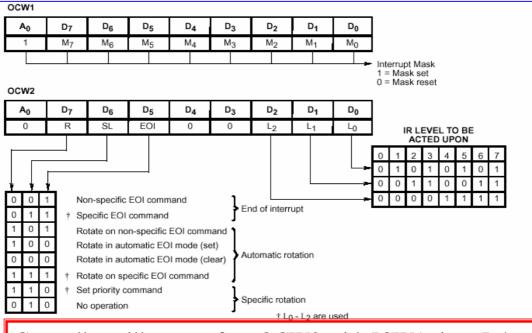

#### OCW1 - OCW2

OCW1 is used to access the contents of the IMR. A READ operation can be performed to the IMR to determine the present setting of the mask. Write operations can be performed to mask or unmask certain bits.

Controller will not confuse OCW2 with ICW1 since D4 = 1

68

#### Example

**ISR PROC FAR**

```

...

MOV AL, 00100000b

OUT 20h, AL

IRET

ISR ENDP

```

What should be OCW1 if interrupt inputs IR0 through IR3 are to be masked and IR4 through IR7 are to be unmasked?

D3D2D1D0 = 1111 D7..D4 = 0 → 00001111 = 0F

What should be OCW2; if priority scheme rotate on non specific EOI issued 101 00000 (since it doesn't have to be specific on certain bit

69

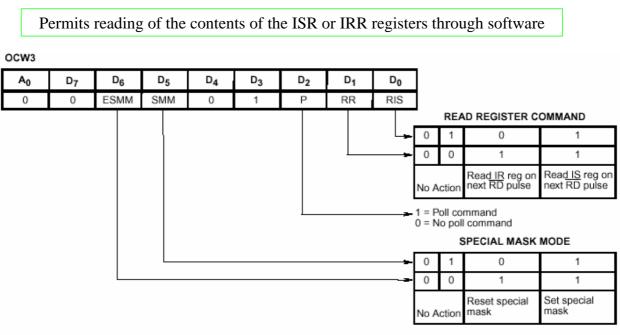

#### OCW3

FIGURE 8. 82C59A OPERATION COMMAND WORD FORMAT

#### Example

Normally when an IR is acknowledged and EOI is not issued, lower priority interrupts will be inhibited.

So the SPECIAL MASK MODE, when a mask bit is set in OCW1, it inhibits further interrupts at that level and enables from all other levels, that are not masked.

MOV AL, 00010000b OUT 21h, AL MOV AL, 01101000b OUT 20h, AL ; mask IRQ4 ; OCW1 (IMR) ; special mask mode ; OCW3

; by masking itself and selecting the special mask mode interrupts on IRQ5 thru IRQ7 will now be accepted by the controller as well as IRQ0 thru IRQ3

## IR7

- Controller does not remember interrupt requests that are not acknowledged

- If an interrupt is requested but no IR bit is found during INTA that is IR is removed before acknowledged, then controller will default to an IR7

- If the IR7 input is used for a legitimate device, the service routine should read the IS register and test to be sure that bit 7 is high

ISR7 PROC FAR MOV AL, 00001011b 20h, AL OUT AL, 20h IN TEST AL, 80h : IS7 set JZ FALSE ; process interrupt here FALSE: IRET ISR7 ENDP

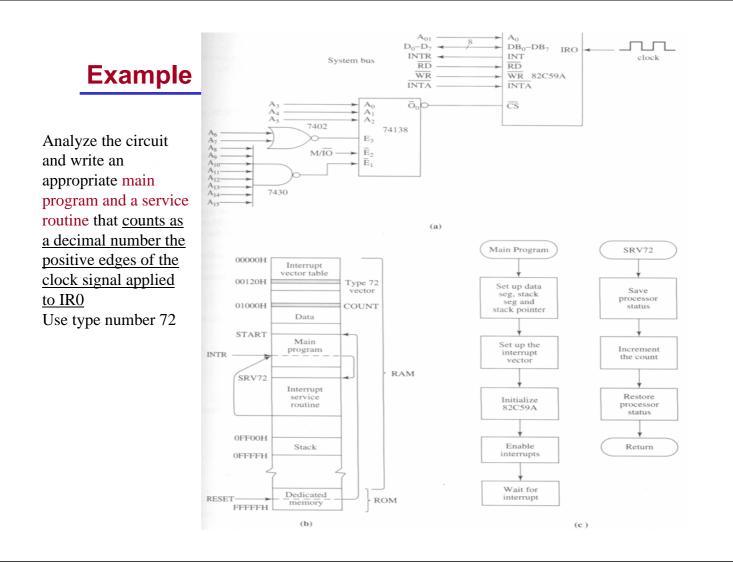

#### Example

- A0 not used

- Two I/O addresses are FF00h and FF02h

- FF00h: ICW1,

- FF02h: ICW2, ICW3, ICW4, OCW1

- ICW1 = 00010011b = 13h

- type number 72 will be used

- ICW2 = 01001000b = 48h

- ICW3 not needed

- nonbuffered and auto EOI

- ICW4 = 03h

- mask all other interrupts but IR0

- OCW1 = 11111110b = FEh

#### Main program and ISR

CLI START: MOV AX, 0 MOV ES, AX MOV AX, 100h MOV DS, AX MOV AX, 0FF0h; stack MOV SS, AX MOV SS, AX MOV SP, 100h ; interrupt install MOV AX, OFFSET SRV72 MOV [ES:120h], AX MOV AX, SEG SRV72 MOV [ES:122h]. AX

75

#### **Example contd**

; initialization

MOV DX, 0FF00h MOV AL, 13h OUT DX, AL MOV DX, 0FF02h MOV AL, 48h OUT DX, AL MOV AL, 03h OUT DX, AL MOV AL, 0FEh OUT DX, AL STI ; wait for interrupt HERE: JMP HERE ; service routine SRV72: PUSH AX MOV AL, [COUNT] INC AL DAA MOV [COUNT], AL POP AX IRET