### **Electrical Engineering**

# Digital Logic Design

A type of "Synchronous Sequential Networks" Sometimes referred to as Finite State Machines FSM

# FSM

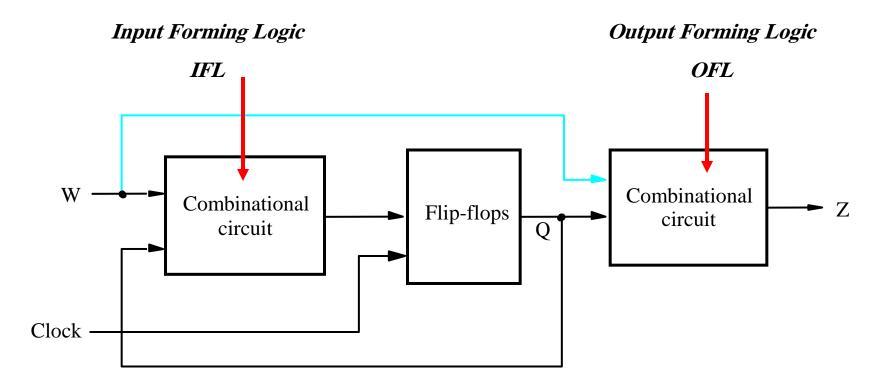

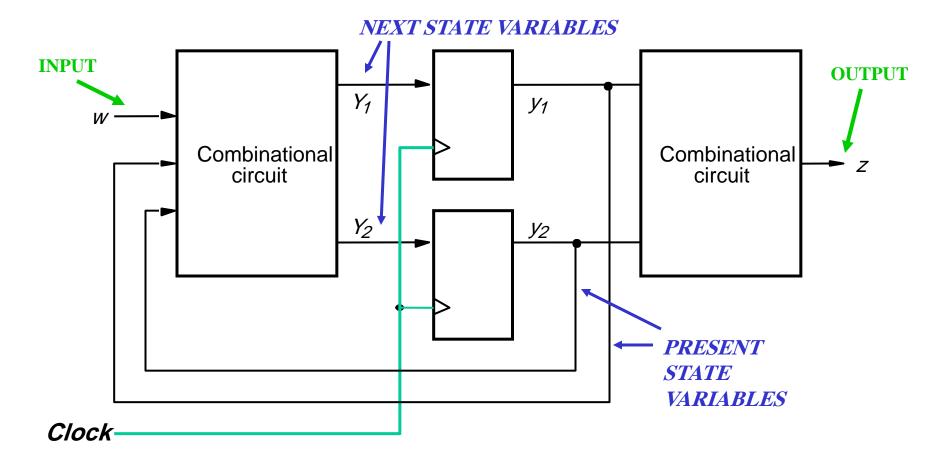

- Finite State Machines are systems that combine Combinational Logic Networks with Memory networks, i.e. flip-flops and are similar to the networks we have been looking at.

- The values of the outputs of the flip-flops are referred to as the *state* of the circuit.

- Under control of the clock signal, the flip-flop outputs change state as determined by the network inputs and the combinational logic that feeds the inputs of these flip-flops.

- In this way, the circuit output varies from one state to another.

#### Figure 1. Here is the general form of a sequential circuit.

### There are Two Types of State Machines

- Mealy Machine (named after George Mealy) in '50's

- Moore Machine (named after Edward Moore who expanded on Mealy concept).

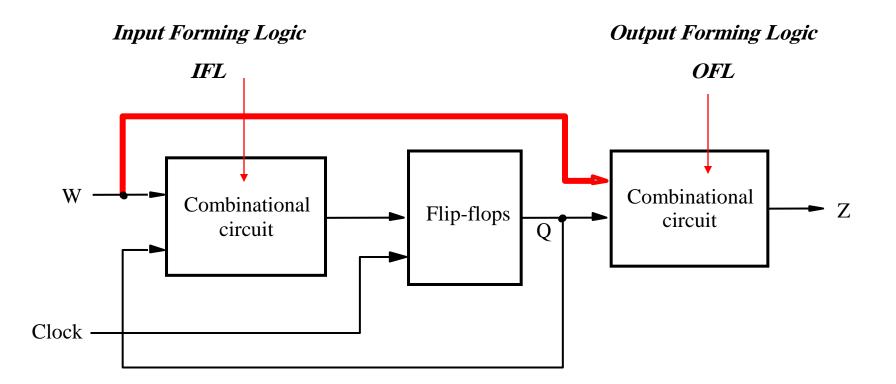

#### **Mealy Machine**

# Input signals **ARE** applied to both the input circuits and the output circuits.

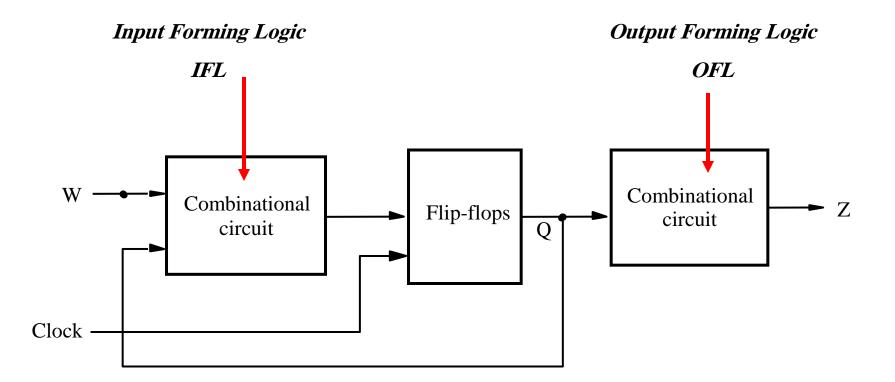

#### **Moore Machine**

# Input signals **ARE NOT** applied to the output circuits – only to the input circuit .

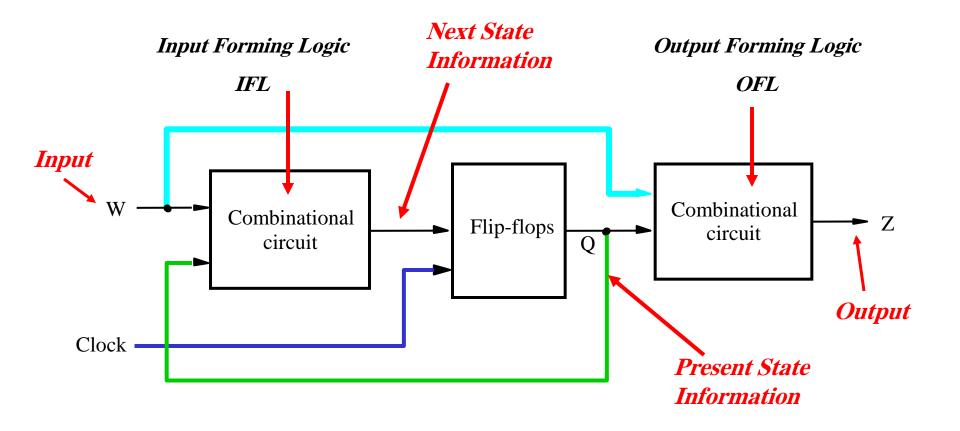

# Operation

- To insure that only one transition, from one state to another state, takes place during one clock cycle, flip-flop's must be EDGE TRIGGERED, and operate on either rising or falling edge.

- The output of the IFL (which is next state information) is formed by the input and current state of the memory

- Thus "state" changes depend on both Input and Present State signals.

- The output of the circuit is formed by either:

- Inputs and present state of flip-flop's (Mealy)

- Present state of flip-flop's (Moore) Dr. Ehab A. H. AL-Hialy

#### Recall the general form of a sequential circuit.

## Lets Look at an example

Before going through the formal process for FSM design/analysis, let's look at an example just to get a little familiar with how these circuits operate and what these circuits do for us.

Begin with a problem definition and create a diagram that depicts the behavior that we want!

Consider a candy vending machine (think of this as a requirements document)

- Requirements for the machine:

- Dispenses a piece of candy if 15¢ is input

- Accepts nickels and dimes

- No change is given

- Two input signals: Nickels (x) and Dimes (y)

- Only one coin entered at a time between clock ticks (clock in this case is a signal resulting from the operation of a gate used to sense coins.

# Vending machine

- On each clock tick, a transition must occur synchronous with the clock.

- Let a circle represent the state

- Let an arc represent a transition between states.

#### Here is how a STATE diagram might look.

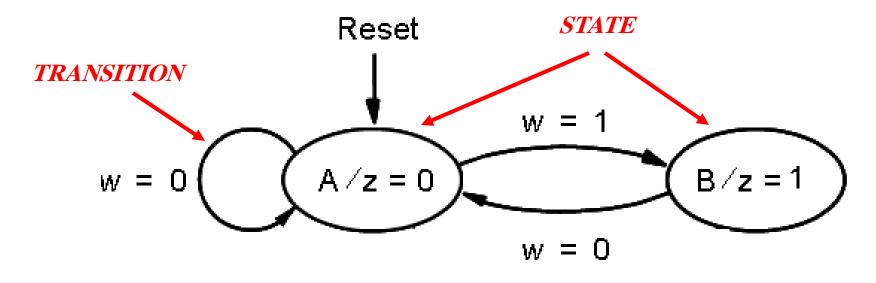

w is an input signal

z is an output signal

State diagram of a simple sequential circuit. Dr. Ehab A. H. AL-Hialy

# Candy vending machine.

(sketch)

- State Definition:

- -A POWER ON State no money entered

- -B Nickel entered no candy

- -C-2 nickels or a dime entered no candy

- -D-15¢ entered dispense candy

- Assume only one coin can be entered at a time.

- If both conditions X and Y could occur at one clock tick, then other paths would have to be considered.

# Now lets work through the formal process for a typical FSM design

- Consider a circuit that

- Has one input,w

- Has one output, z

- Z=1 if w=1 for 2 or more immediately proceeding consecutive clock cycles (rising edge)

- Z = 0 if w does not equal 1 for 2 immediately proceeding consecutive clock cycles

- Circuits that detect a specific bit pattern on the input are referred to as sequence detectors.

- It is apparent that z cannot depend solely on present state • of w.

- Our job is to design a circuit that satisfies the above requirement.

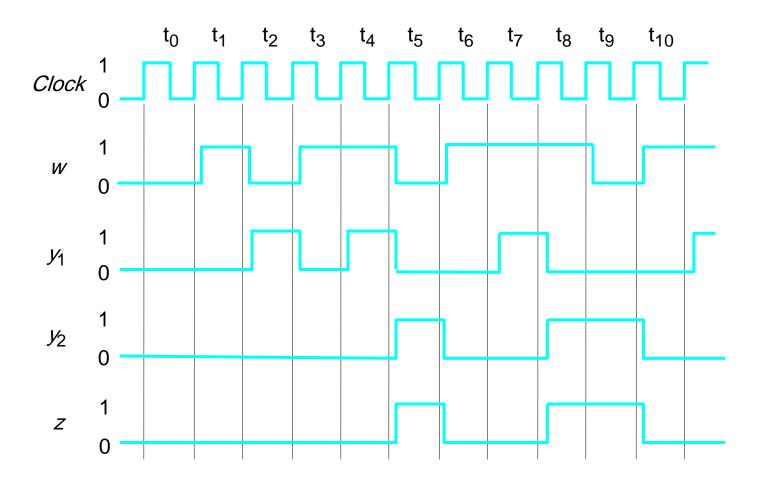

| Here is the formal description |       |       |       |    |    |    |                |    |                |    |                 |

|--------------------------------|-------|-------|-------|----|----|----|----------------|----|----------------|----|-----------------|

| of the sequence detector       |       |       |       |    |    |    |                |    |                |    |                 |

|                                | 1     | 1     | t     | 1  | 1  | 1  | 1              | 1  | 1              | 1  | 1               |

| Clockcycle:                    | $t_0$ | $t_1$ | $t_2$ | t3 | t4 | t5 | t <sub>6</sub> | t7 | t <sub>8</sub> | t9 | t <sub>10</sub> |

|                                | 0     |       |       |    |    |    | 1              |    | 1              | 0  | 1               |

| Z:                             | 0     | 0     | 0     | 0  | 0  | 1  | 0              | 0  | 1              | 1  | 0               |

If z depended on *w* alone, then it would not be possible for z to be equal to two different values for a single value of the input, or the same value of z for different values of *w*

Figure 2. Sequences of input and output signals.

Here is the STATE diagram that we've come up with that satisfies our specification for the sequence detector.

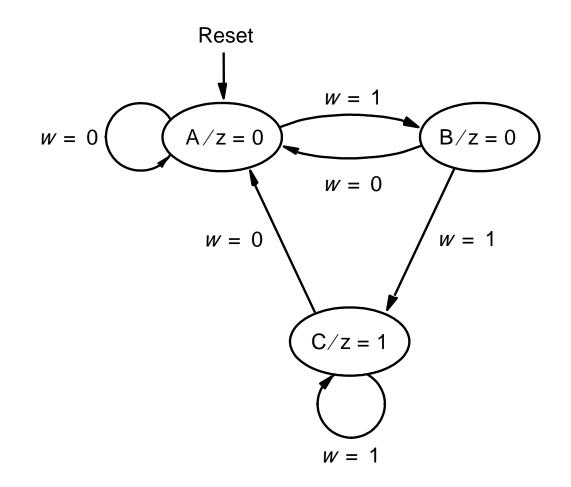

Reset *w* = 1 A/z = 0B/z = 0W = 0W = 0*w* = 1 W = 0C/z = 1*w* = 1

Figure 3. State diagram of a simple sequential circuit. Dr. Ehab A. H. AL-Hialy

17

Remember, we have to design a circuit that satisfies the description we came up with earlier.

# Next Step

- The next step in the design is to create a tabular listing of the action that is depicted in the state diagram.

- This is called a STATE TABLE

#### Here is the STATE diagram that we came up with

| Present | Next  | Output |   |  |

|---------|-------|--------|---|--|

| state   | W = 0 | W = 1  | Z |  |

| A       | А     | В      | 0 |  |

| B       | А     | С      | 0 |  |

| C       | А     | С      | 1 |  |

Figure 4. State table for the sequential circuit in Figure 3. Dr. Ehab A. H. AL-Hialy

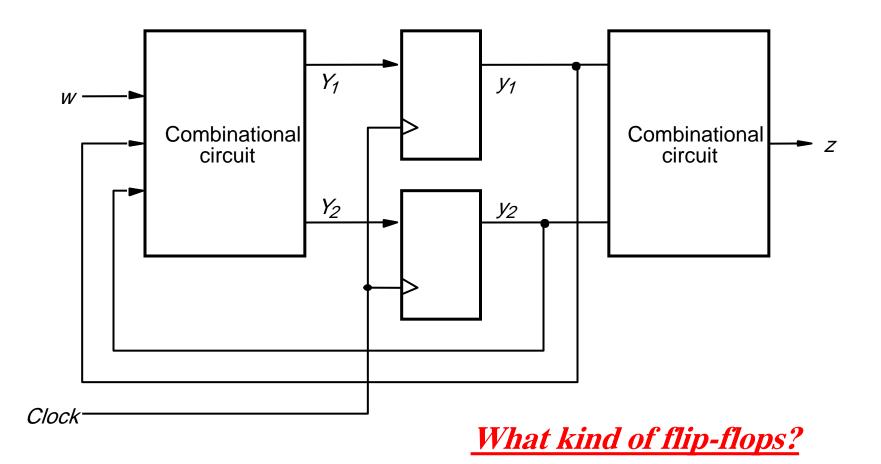

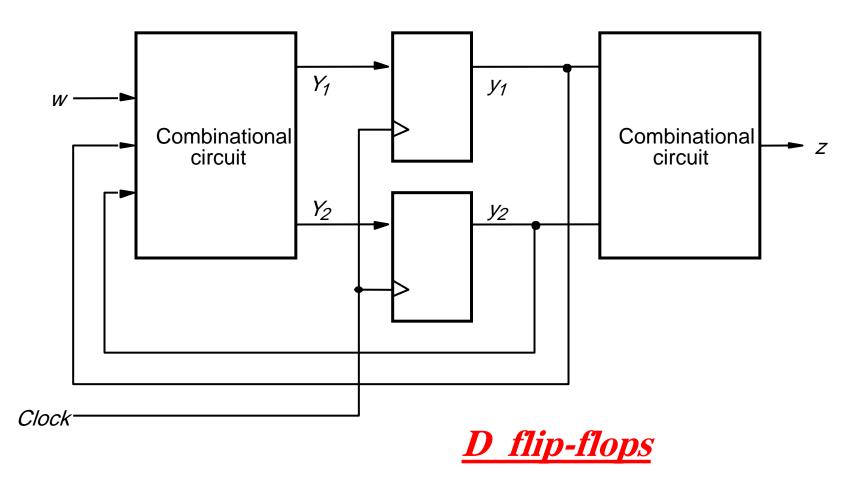

# Number of Flip-Flops

• Since each Flip=flop can represent 2 states, since we have 3 states, we need 2 flip-flops.

<u>Mealy or Moore ?</u>

Figure 5. A general sequential circuit with input *w*, output *z*, and two state flip-flops.

Figure 5. A general sequential circuit with input w, output z, and two state flip-flops. 24

# Next Step

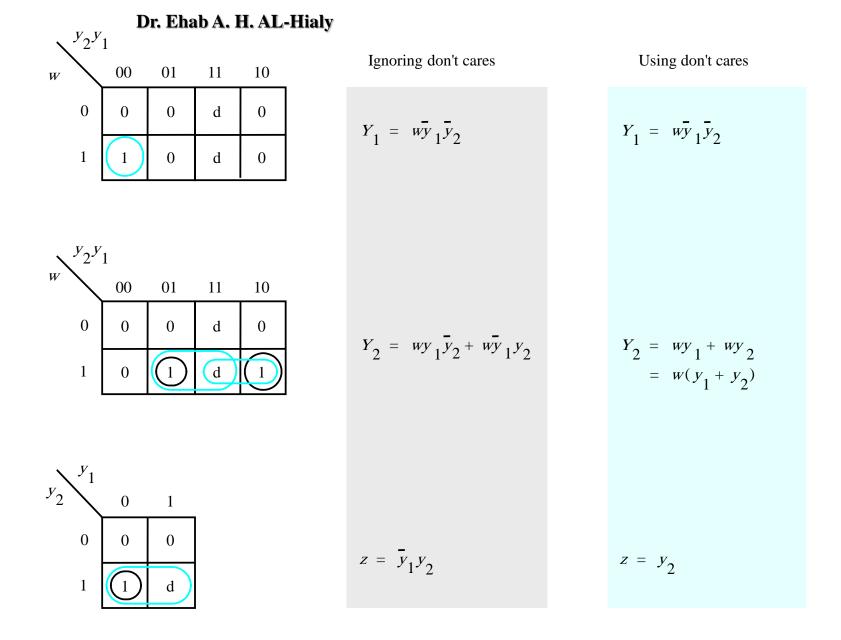

• Design the combinational logic circuit that will generate the

### **NEXT STATE VARIABLES** and the **OUTPUT**

Since the output is solely determined by the output of the memory FlipFlops (present state information) it is a Moore Machine.

Figure 5. A general sequential circuit with input *w*, output *z*, and two state flip-flops.

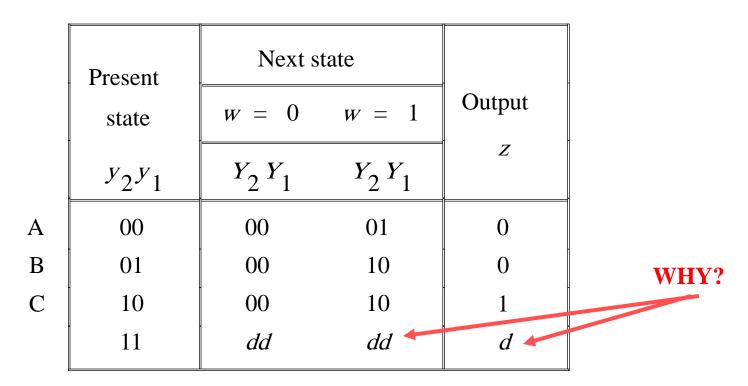

# Here is where we assign the flip-flop outputs to the various states.

## *Note that this is just like the truth tables we developed for the combinational logic circuits.*

Figure 6. State-assigned table for the sequential circuit in Dr. EFaigure A4-Hialy

Figure 7. Derivation of logic expressions for the sequential circuit in Figure 6.

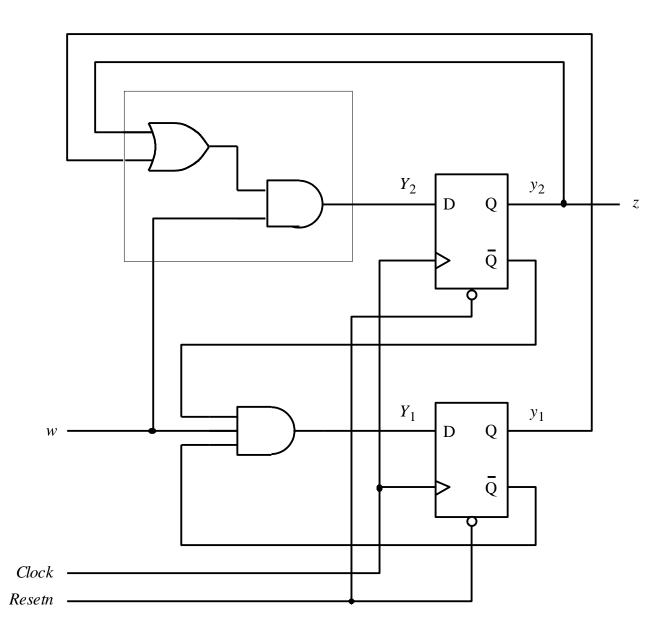

Figure 8. Final implementation  $A_{1,0}$  the sequential circuit derived in Figure 7.

Figure 9. Timing diagram for the circuit in Figure 8. Dr. Ehab A. H. AL-Hialy

30

# Summary of Design Steps in the Design of a FSM

- 1. Obtain specification of desired behavior

- 2. Select start state

- 3. Determine number of states needed

- 4. Use a state diagram to keep track of states

- 5. Account for all I/O conditions

- 6. Identify when machine moves from state to state

- 7. Create state table from state diagram

- 8. Minimize number of states

- 9. Decide on number of state variables

- 10. Perform state assignments

Summary of Design Steps in the Design of a FSM (con't)

Chose type of flip-flop

Derive next state logic expressions (inputs to flip-flops)

Derive logic expressions for outputs

14. Implement circuits